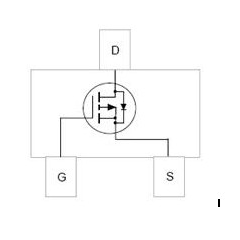

D-FET ay nasa 0 gate bias kapag ang pagkakaroon ng channel, maaaring magsagawa ng FET; Ang E-FET ay nasa 0 gate bias kapag walang channel, hindi maaaring magsagawa ng FET. ang dalawang uri ng FET na ito ay may kanya-kanyang katangian at gamit. Sa pangkalahatan, ang pinahusay na FET sa high-speed, low-power circuits ay napakahalaga; at gumagana ang device na ito, ito ang polarity ng gate bias voltage at alisan ng tubig boltahe ng pareho, ito ay mas maginhawa sa disenyo ng circuit.

Ang tinatawag na pinahusay na paraan: kapag ang VGS = 0 tube ay isang cut-off na estado, kasama ang tamang VGS, ang karamihan ng mga carrier ay naaakit sa gate, kaya "pinahusay" ang mga carrier sa rehiyon, na bumubuo ng isang conductive channel. Ang n-channel na pinahusay na MOSFET ay karaniwang isang kaliwa-kanang simetriko topology, na siyang P-type na semiconductor sa pagbuo ng isang layer ng SiO2 film insulation. Ito ay bumubuo ng isang insulating layer ng SiO2 film sa P-type semiconductor, at pagkatapos ay nagkakalat ng dalawang mataas na doped N-type na rehiyon sa pamamagitan ngphotolithography, at humahantong sa mga electrodes mula sa rehiyon ng N-type, isa para sa drain D at isa para sa source S. Ang isang layer ng aluminum metal ay nilagyan ng insulating layer sa pagitan ng source at ang drain bilang gate G. Kapag VGS = 0 V , medyo kakaunti ang mga diode na may back-to-back diodes sa pagitan ng drain at source at ang boltahe sa pagitan ng D at S ay hindi bumubuo ng kasalukuyang sa pagitan ng D at S. Ang kasalukuyang sa pagitan ng D at S ay hindi nabuo sa pamamagitan ng boltahe na inilapat .

Kapag idinagdag ang boltahe ng gate, kung 0 < VGS < VGS(th), sa pamamagitan ng capacitive electric field na nabuo sa pagitan ng gate at substrate, ang mga butas ng polyon sa P-type semiconductor malapit sa ilalim ng gate ay tinataboy pababa, at lumilitaw ang isang manipis na layer ng pag-ubos ng mga negatibong ion; sa parehong oras, ito ay maakit ang mga oligons doon upang lumipat sa ibabaw na layer, ngunit ang bilang ay limitado at hindi sapat upang bumuo ng isang conductive channel na nakikipag-ugnayan sa alisan ng tubig at pinagmulan, kaya ito ay hindi pa rin sapat sa Formation ng alisan ng tubig kasalukuyang ID. karagdagang pagtaas VGS, kapag VGS > Ang VGS (th) (VGS (th) ay tinatawag na turn-on na boltahe), dahil sa oras na ito ang boltahe ng gate ay medyo malakas, sa P-type na semiconductor surface layer malapit sa ilalim ng gate sa ibaba ng pagtitipon ng higit pa electron, maaari kang bumuo ng isang trench, ang alisan ng tubig at ang pinagmulan ng komunikasyon. Kung ang boltahe ng pinagmumulan ng alisan ng tubig ay idinagdag sa oras na ito, ang kasalukuyang alisan ng tubig ay maaaring mabuo ng ID. Ang mga electron sa conductive channel ay nabuo sa ibaba ng gate, dahil sa carrier hole na may P-type semiconductor polarity ay kabaligtaran, kaya ito ay tinatawag na anti-type na layer. Habang patuloy na tumataas ang VGS, patuloy na tataas ang ID. ID = 0 sa VGS = 0V, at ang drain current ay nangyayari lamang pagkatapos ng VGS > VGS(th), kaya, ang ganitong uri ng MOSFET ay tinatawag na enhancement MOSFET.

Ang kontrol na relasyon ng VGS sa drain current ay maaaring ilarawan ng curve iD = f(VGS(th))|VDS=const, na tinatawag na transfer characteristic curve, at ang magnitude ng slope ng transfer characteristic curve, gm, sumasalamin sa kontrol ng kasalukuyang alisan ng tubig sa pamamagitan ng boltahe ng pinagmulan ng gate. ang magnitude ng gm ay mA/V, kaya ang gm ay tinatawag ding transconductance.